# **IBIS** and Power Delivery Systems

Jiang, Xiangzhong Li, Jinjun Zhang, Shengli

**Huawei Technologies, China**

#### Content

- 1. IBIS history in Huawei

- 2. Model Platform in Huawei

- 3. IBIS Validation

- 4. HUAWEI spice circuit model library

- 5. HUAWEI Simulation platform of power integrity

- 6. Conclusion

- 7. Reference

# IBIS history in Huawei

➤ A accurate Simulate Model is first element of successful SI, and the difficult step.

| •1999 | SI dept. founded                                       |

|-------|--------------------------------------------------------|

| •2000 | Test board and simulate arithmetic study               |

| •2001 | Mr. Bob Ross visit Huawei and lecture; IBIS Membership |

| •2001 | Modeling Group foundedTrack Industry Model development |

| •2003 | lbischk4 fund                                          |

| •Now  | Asian IBIS Summit 2005                                 |

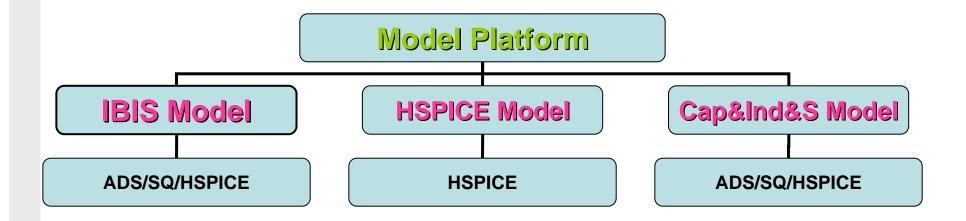

#### 2. Model Platform in Huawei

➤ Total simulation Model solution

#### 3. IBIS Validation

#### >Ibischk3

- ◆Syntax Errors and Warnings

- **♦**Common Errors and Warnings

- Structural Errors and Warnings

- ◆Non-monotonicity Warnings

- ◆Extraction Errors and Warnings

#### 3. IBIS Validation

- ➤ IBIS file check(correct&Completeness,Databook)

- **♦IBIS** Properties

- **♦**Component Properties [pin]list

- **♦**Package&pin Properties

- •C\_pin L\_pin R\_pin;

- **♦**Model\_type

- •C\_comp

- •[Voltage Range]

- •Vinh,Vinl

- •Vmeas Vref Rref Cref

- Max/Min Data condition

- •VI Properties

- •VT Properties

# 3. IBIS Validation

- **≻**Simulate

- **♦** Spice Correlation

- ◆ Voltage Swings[high/low,over]

- **◆**Timing Test Load Response

#### ➤ Measure

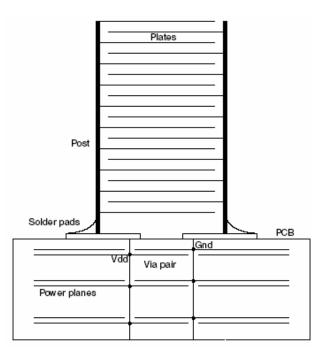

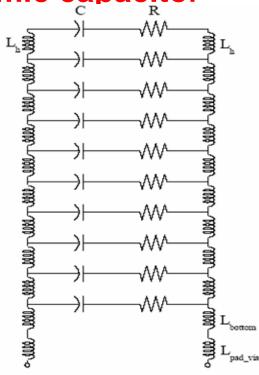

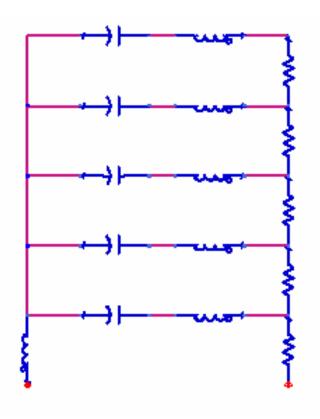

#### > Distributed circuit model of ceramic capacitor

Cross section of discrete capacitor mounted on PCB power planes

Distributed circuit model for SPICE derived from construction of ceramic capacitor

➤ Element values model was extracted from measured sparameter based on Monte Carlo method

The spice netlist of 0.01uF ceramic capacitor

```

.subckt C 08070247 1 5

+ esr=lm loopInductance=ln

lloop 1 2 loopInductance

L11 2

За

4.241151e-010 h

C11 3a

32a

8.785720e-010 f

R11 32a

7.684703e-001 ohm

Lrl 4a

3

4.241151e-010 h

L12 3a

5a

1.439540e-011 h

CZ

31a

8.785720e-010 f

31a

R2

7.684703e-001 ohm

1.439540e-011 h

L13

1.439540e-011 h

8.785720e-010 f

7.684703e-001 ohm

1.439540e-011 h

L14

1.439540e-011 h

C4

299

8 785720e-010 f

R4

10a

7.684703e-001 ohm

Lr4

10a

1.439540e-011 h

L15

11a

1.439540e-011 h

288

8.785720e-010 f

289

12a

7.684703e-001 ohm

10a

1.439540e-011 h

13a

1.439540e-011 h

13a

8.785720e-010 f

14a

7.684703e-001 ohm

Lr6

14a

12a

1.439540e-011 h

13a

15a

1.17

1.439540e-011 h

8.785720e-010 f

16a

7.684703e-001 ohm

16a

14a

1.439540e-011 h

1.439540e-011 h

15a

8.785720e-010 f

7.684703e-001 ohm

Lr8 18a

16a

1.439540e-011 h

L19 17a

19a

1.439540e-011 h

C9

19a

749

8.785720e-010 f

20a

7.684703e-001 ohm

D9

24a

Lr9 20a

18a

1.439540e-011 h

L110 19a

21a

1.439540e-011 h

C10 21a

238

8.785720e-010 f

RIO

23a

22a

7.684703e-001 ohm

Lr10 22a

20a

1.439540e-011 h

rl 3 4 esr // esr in ohms

rdum 2 3 10Meg // resistor to make dc path

vsense 4 5 0 ac=0

.ends C_08070247

```

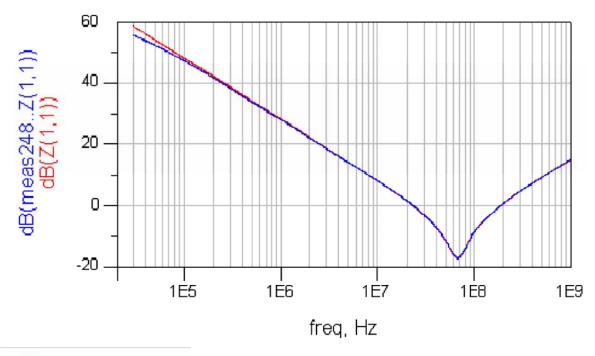

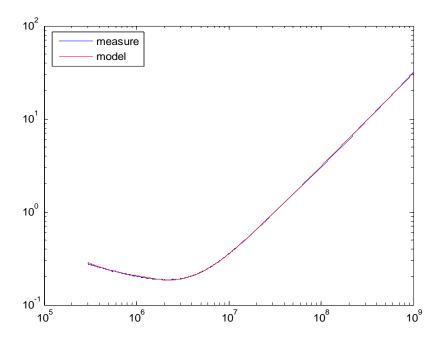

➤ Distributed circuit model simulation compared to measured 0.01uF capacitor

**≻**Spice circuit model of 10uF Tantalum capacitor

# ➤The spice netlist of 10uF Tantalum capacitor

```

.subckt C 08020059 1 5

+ esr=lm loopInductance=ln

lloop 1 2 loopInductance // loop or mounted inductance in henries cl 2 la capacitance

1.328655e-009 h

Cl 3a

32a

2.090239e-006 f

L1 32a

4.893012e-010 h

4a

2.133079e-001 ohm

C2 3a

31a 3.609295e-006 f

6a 1.015527e-009 h

L2 31a

R2 6a

3.549960e-001 ohm

3a

30a 1.426664e-007 f

L3 30a

1.952736e-009 h

R3 8a

8.641232e-001 ohm

C4 3a

29a 5.113291e-007 f

L4 29a

10a 8.165504e-010 h

R4 10a

7.889731e-001 ohm

C5 3a

28a

1.839965e-007 f

L5 28a

12a

6.076517e-010 h

R5 12a

10a

1.088326e+000 ohm

rl 3 4 esr // esr in ohms

rdum 2 3 10Meg // resistor to make dc path

vsense 4 5 0 ac=0

.ends C 08020059

```

Element values model was extracted from measured s-parameter based on Monte Carlo method

**HUAWEI TECHNOLOGIES**

# 5. HUAWEI Simulation platform of power integrity

Cadence SQPI based two-dimension transmission line theory

S-parameter:

Spice model: high-efficiently

Ansoft Siwave Based electromagnetic theory

S-parameter

# 5. HUAWEI Simulation platform of power integrity

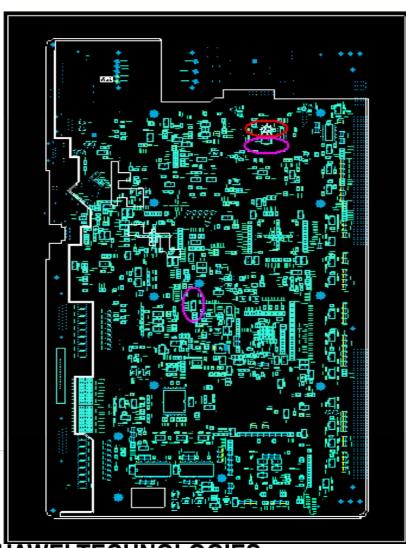

**≻Simulation of Power integrity for one product**

**Total pins: 13022 pins**

Stackup: 12 layers

**Power consumption: 3.3VX20A**

**HUAWEI TECHNOLOGIES**

# 5. HUAWEI Simulation platform of power integrity

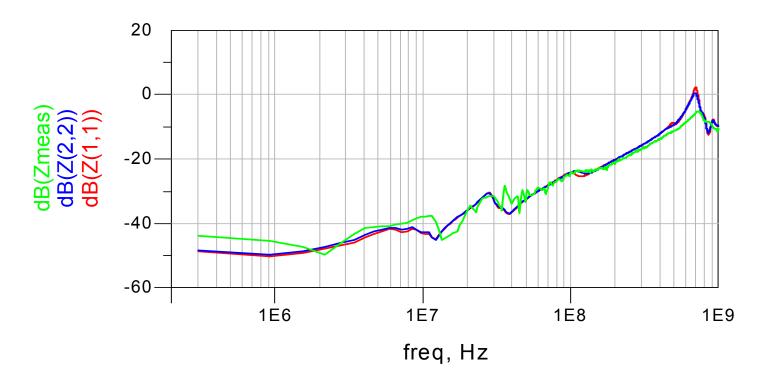

>Simulated and measured impedance of power network for the product

Red: s-parameter; Blue: spice mode; Green: measurement

#### 6. Conclusion

- •HUAWEI have Validated IBIS model Library.

- •HUAWEI hold completed and accurate spice model library of passive component;

- •Simulation platform of power integrity based on spice model library has been founded;

- •The simulated impedance proved to be consistent with measurement and can be used to solve the power noise problem of product.

#### 7. Reference

- 1. Stephen Peters, "I/O BUFFER MODELING COOKBOOK", Intel, 1997

- 2. Bob Ross, "Inspecting IBIS Models", Mentor Graphics, 1998

- 3. Roy Leventhal, "How to Use the IBIS Model", 3COM, 1999

- 4. 3COM, "3COM IBIS MODEL STANDARD", 3COM, 1999

- 5. Syed B.Huq, "Effective Signal Integrity Analysis using IBIS Models", Cisco Systems, 2000

- 6. Arpad.muranyi, "Introduction to IBIS models", intel, 2000

- 7. IBIS Forum, "ibis\_quality\_checklist", 2002

- 8. Eckhard Lenski, "IBIS-models today, their patameters and their accuracy", Siemens AG,2002

- 9. Barry Katz, "IBIS Quality Committee Report", Sisoft, 2002